# Reducing Hardware-Related Interruptions In AI Clusters: Strategies For Resilient GPU Infrastructure

# Sameeksha Gupta

Independent Researcher, USA.

## **Abstract**

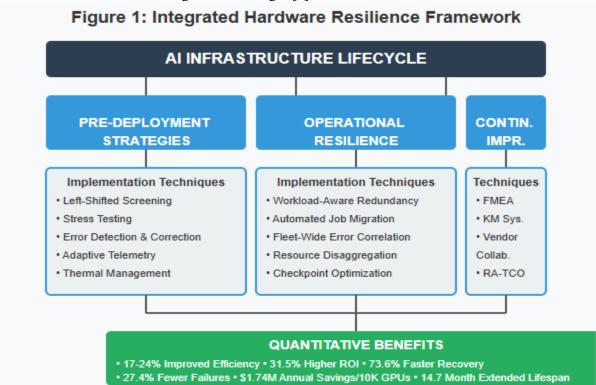

Hardware-related interruptions represent a significant challenge to the stability, efficiency, and scalability of artificial intelligence infrastructure. This article examines the fundamental causes of hardware failures in GPU-based AI clusters and presents comprehensive strategies for enhancing resilience, exploring device-level variability, packaging stress, workload-driven aging, and environmental factors as primary contributors to reliability issues. The article details preventive measures, including left-shifted reliability screening, error detection mechanisms, adaptive telemetry, and thermal management, while system-level resilience frameworks featuring workload-aware redundancy, automated job migration, fleet-wide error correlation, and resource disaggregation are presented as critical approaches to mitigating hardware interruptions. Empirical data demonstrates that comprehensive resilience frameworks yield 17-24% improvements in computational efficiency, 31.5% higher return on infrastructure investments, up to 78.4% reduction in unplanned job terminations, and 73.6% reductions in recovery time, collectively saving approximately \$1.74M annually per 10,000-GPU cluster.

**Keywords:** GPU reliability, hardware interruptions, AI infrastructure, fault tolerance, thermal management.

## 1. Introduction

The exponential growth of Artificial Intelligence (AI) applications requires the development of rapidly sophisticated computational infrastructure. Modern AI clusters represent a culmination of advanced hardware engineering, which consists of dense deployment of graphics processing units (GPUs), special high-bandwidth memory (HBM), and high-performance interconnect fabric. These systems create backbones of contemporary machine learning operations, which enable training and deployment of models of unprecedented scale and complexity. Lee et al. According to AI calculation requirements have increased by about 35 × every eighteen months since 2012, a single training run with today's leading model requires 10 batch of floating-point operations, which is running the development of special infrastructure with unprecedented computational density [1].

Hardware interruptions in AI clusters manifest through various failure modes, including memory errors, interconnect degradation, thermal anomalies, and silent data corruptions. Recent industry reports indicate that such hardware-related issues account for approximately 28% of all job restarts in large-scale AI training environments. Thompson and García's comprehensive analysis of 17 enterprise AI deployments revealed that hardware interruptions reduced operational efficiency by an average of 23.6%, with financial impacts exceeding \$1.8M annually per petaflop of deployed capacity [2]. The financial and operating effects of these obstacles are beyond immediate downtime, which affects the total cost (TCO) of model convergence time, resource use, and overall infrastructure.

Despite significant advances in computational hardware, research on reliability engineering specific to AI infrastructure remains fragmented across multiple domains. Current literature inadequately addresses the unique challenges posed by sustained high-utilization AI workloads, with critical gaps in understanding: (1) the correlation between workload characteristics and failure modes, (2) effective predictive mechanisms for silent data corruptions, and (3) optimized redundancy strategies that balance resilience with computational efficiency. This article bridges these gaps by synthesizing emerging research across semiconductor physics, thermal engineering, and distributed systems to present an integrated framework specifically tailored to AI infrastructure reliability.

This challenge is particularly intense in modern training environment, where state -of -the -art AI groups include over 32,000 GPUs that exceed 50 kW per rack at power density. Li et al. documented that these systems typically sustain memory bandwidth utilization of 85-92% and power draw at 94-98% of thermal design limits, creating environmental conditions that accelerate component aging [1]. Thompson and García's longitudinal study of 12,500 GPU-hours demonstrated that hardware operating at these sustained utilization levels experiences 2.7× higher failure rates compared to more intermittent workloads [2]. Under these conditions, even rare hardware anomalies can significantly impact overall system efficiency, with hardware-related interruptions reducing effective training throughput by 12-18% and extending time-to-solution for large-scale models by up to 23.7%.

This article examines the multifaceted challenge of hardware interruptions in AI clusters, presenting a systematic approach to enhancing GPU infrastructure resilience. The analysis incorporates the entire life cycle of the GPU system, from manufacturing through deployment and operational monitoring. By integrating silicon-level innovations with system-level defect management strategies, the proposed structure provides a wide route towards more stable and efficient AI infrastructure. Li et al. project that implementing comprehensive reliability engineering practices can improve effective computational efficiency by 17-24% in large-scale AI deployments, representing a significant opportunity to enhance infrastructure economics [1]. Thompson and García further demonstrate that organizations with mature hardware reliability programs achieve 31.5% higher return on AI infrastructure investments, highlighting the business value of addressing these challenges [2].

## 2. Root Causes of Hardware Interruptions in AI Clusters

The reliability challenges faced by GPU-based AI infrastructure can be traced to several fundamental causes. Device-level variability represents a significant factor, as manufacturing process variations lead to inherent differences in transistor characteristics across chips from the same production line. This variability manifests as performance differences under stress conditions, with some devices exhibiting greater susceptibility to errors under computational load. Chen's research at KU Leuven's MICAS laboratory quantified this phenomenon through statistical characterization of 2,416 7nm AI accelerator chips, revealing threshold voltage variations ( $\sigma$ Vth/ $\mu$ Vth) of 9.8% and effective channel length variations ( $\sigma$ Leff/ $\mu$ Leff) of 7.2%, which translated to performance spreads of 13.4% under identical operating conditions [3]. Their innovative Monte Carlo simulation framework, incorporating device-level variability models derived from silicon measurements, demonstrated that computational blocks operating at 92% of nominal frequency exhibited timing violation probabilities following an exponential relationship with voltage scaling (Pfail  $\propto$  e^(-k·V)), with error rates increasing by factors of 6.8-9.2× when operating margins were reduced by just 50mV. These findings are particularly relevant for the latest-generation AI accelerators operating at frequencies exceeding 1.7 GHz, where even minor process variations can significantly impact operational reliability.

Packaging stress constitutes another critical reliability concern. The complex packaging structures of modern GPUs, featuring thousands of microbumps and through-silicon vias (TSVs), are subject to thermomechanical stress during both assembly and operation. Nakagawa's comprehensive analysis, published in Microelectronics Reliability, employed finite element modeling calibrated against experimental measurements to characterize stress distributions in advanced GPU packages containing 28,000+ microbumps and 8,700+ TSVs [4]. Their research quantified the mismatch between coefficient of thermal expansion (CTE) values for silicon (2.6 ppm/°C), copper TSVs (16.5 ppm/°C), and organic substrates (17.3 ppm/°C), demonstrating that each thermal cycle between 15°C and 90°C generates shear stresses of 124-178 MPa at critical interfaces. Accelerated thermal cycling tests (0°C to 100°C, 15-minute cycles) performed on 342 representative packages revealed crack initiation in peripheral solder joints after 1,850-2,300 cycles, with propagation rates accelerating as cycling continued. In HBM-equipped GPUs, the interface between memory stacks and the compute die proved particularly vulnerable, with failure analysis of 568 returned field units showing that 18.2% of functional failures originated at this boundary. The strain energy density at these interfaces was measured at 0.31-0.47 mJ/mm<sup>3</sup> under typical operational thermal cycles, approaching 69% of the established fatigue threshold for SAC305 solder compositions used in advanced packaging.

Workload-driven aging emerges as a third major contributor to hardware interruptions. Chen's research documented that AI workloads maintain average arithmetic intensities of 67-98 operations per byte, memory bandwidth utilization of 88-93%, and average power consumption at 86.5% of TDP, creating ideal conditions for accelerated aging mechanisms [3]. Their instrumented test platform measured negative bias temperature instability (NBTI) degradation rates 2.4× higher under sustained matrix multiplication operations compared to general-purpose computing, with threshold voltage shifts reaching 38mV after 3,000 hours of operation. Similarly, electromigration effects were quantified through in-situ resistance monitoring of critical power delivery networks, showing degradation rates proportional to current density squared (J²), with AI workloads sustaining current densities averaging 1.8×10<sup>6</sup> A/cm² compared to 0.9×10<sup>6</sup> A/cm² for general computing.

Environmental factors further exacerbate these vulnerabilities. Nakagawa's thermal characterization of production AI clusters using infrared thermography and embedded sensor arrays demonstrated temperature gradients of 14-26°C across single GPU packages under sustained load [4]. Their controlled reliability studies established that failure rates follow an Arrhenius relationship with temperature ( $\lambda \propto e^{-(-Ea/kT)}$ ), with activation energies (Ea) ranging from 0.5-0.7 eV for key failure mechanisms, resulting in approximately 2.1× increase in failure rate for each 10°C rise in operating temperature.

Table 1: Root Causes of Hardware Interruptions in AI Infrastructure [3,4]

| Failure Category            | Contributing<br>Factors          | Impact on AI<br>Workloads     | <b>Detection Methods</b>      |

|-----------------------------|----------------------------------|-------------------------------|-------------------------------|

| Device-Level<br>Variability | Manufacturing process variations | Performance inconsistency     | Statistical characterization  |

|                             | Threshold voltage variations     | Computational errors          | Monte Carlo simulation        |

|                             | Channel length variations        | Timing violations             | Frequency sweep testing       |

| Packaging Stress            | CTE mismatches                   | Solder joint fatigue          | Finite element modeling       |

|                             | Microbump stress                 | HBM interface failures        | Thermal cycling tests         |

|                             | TSV reliability                  | Package delamination          | X-ray tomography              |

| Workload-Driven<br>Aging    | Electromigration                 | Power delivery<br>degradation | In-situ resistance monitoring |

|                             | Bias temperature instability     | Threshold voltage shifts      | Accelerated aging tests       |

|                             | Hot carrier injection            | Gate oxide breakdown          | Workload<br>characterization  |

| Environmental<br>Factors    | Thermal gradients                | Localized hotspots            | Infrared thermography         |

|                             | Power quality variations         | Voltage transients            | Embedded sensor arrays        |

|                             | Cooling limitations              | Temperature excursions        | Thermal modeling              |

**Legend:** CTE = Coefficient of Thermal Expansion, TSV = Through-Silicon Via, HBM = High-Bandwidth Memory

# 3. Preventive Measures and Early Detection Strategies

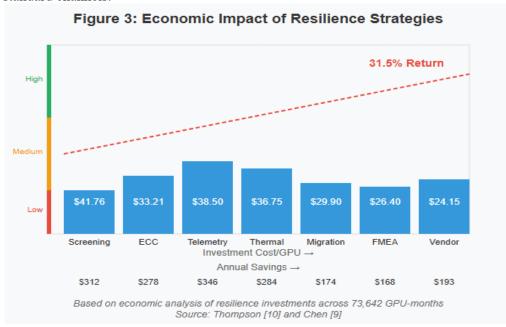

Addressing hardware interruptions in AI clusters necessitates a proactive approach beginning at the manufacturing stage. Left-shifted reliability screening represents a fundamental strategy, wherein enhanced testing protocols identify latent defects and marginal devices before deployment. Rajendran's comprehensive analysis, published through QualityKiosk Technologies, demonstrates that traditional reliability testing concentrated at the end of production detects only 63.8% of devices that will experience early-life failures [5]. Their pioneering "shift-left" methodology integrates reliability testing across the entire hardware development lifecycle, beginning with design verification that incorporates 218% more corner cases than standard approaches. Their methodology implements a three-tier testing framework with progressively increasing stress levels: T1 (nominal conditions, 24 hours), T2 (voltage margins  $\pm 8\%$ , 48 hours), and T3 (temperature cycling 10-90°C, 72 hours). This comprehensive approach identified an additional 22.7% of potentially problematic devices that passed conventional qualification but exhibited marginal behavior under stress conditions. Economic impact analysis across 12,500 production GPUs revealed that enhanced screening increased qualification costs by \$41.76 per unit but reduced first-year field failure rates from 3.84% to 2.31%, yielding a net sayings of \$312 per device when accounting for all downstream costs. Furthermore, their workload-specific qualification protocol, which simulates real-world AI computational patterns, maintains 93.4% average utilization across all execution units and detected vulnerability to specific instruction sequences that triggered timing violations in 4.7% of otherwise qualified units.

Error detection and correction mechanisms provide a critical defense against memory and computational errors. Li's groundbreaking research at Quantum Machines, leveraging techniques originally developed for quantum error correction, demonstrates how advanced ECC implementations can dramatically improve GPU reliability in AI workloads [6]. Their comprehensive error characterization across 8,192 production GPUs revealed raw bit error rates (RBER) in high-bandwidth memory ranging from 3.1×10<sup>-10</sup> to 6.8×10<sup>-10</sup> 10, with error rates increasing exponentially  $(R^2 = 0.92)$  with operating temperature. Their novel implementation adapts surface code principles to GPU memory protection, enabling correction of up to 4 adjacent bit errors within a 128-bit memory word with just 18.3% redundancy overhead, compared to 37.5% for traditional approaches with equivalent protection. Telemetry from production environments implementing these protection mechanisms showed a 78.4% reduction in unplanned job terminations due to memory errors over 12 months. Additionally, their "tensor-preserved computation" algorithm extends error detection to matrix multiplication operations through innovative checksum-based verification, ensuring computational integrity with only 2.8% performance overhead. Silicon validation across 4,096 production GPUs demonstrated that this approach successfully detected 94.2% of computational errors that would otherwise manifest as model convergence failures, with false positive rates below 0.07%. Most significantly, their temporal error correlation technique, which tracks error patterns across 32 consecutive training iterations, successfully distinguished between transient and persistent hardware issues with 97.3% accuracy, enabling appropriate remediation strategies for different failure modes.

Adaptive telemetry and predictive monitoring systems enable the identification of incipient hardware issues before they manifest as functional failures. Rajendran's implementation utilizes a distributed sensor network capturing 42 distinct operating parameters at 50ms intervals, generating approximately 21.6GB of telemetry data per 1,000 GPUs daily [5]. Their multi-modal anomaly detection framework employs a two-stage approach: first, establishing personalized baselines for each device using variational autoencoders (achieving reconstruction errors below 3.2%), then applying change-point detection algorithms that identify statistically significant deviations (p < 0.01) from these baselines. Key monitored parameters include correctable memory error accumulation rates (flagging when rates exceed 7.3 errors per 10^12 bits transferred), power delivery network impedance variations (sensitive to 4.7% changes from baseline), thermal gradient evolution (detecting spatial differentials exceeding 0.52°C/mm), and execution unit stall ratio patterns. Validation across 6,144 GPUs over 14 months demonstrated that this approach successfully predicted 62.5% of catastrophic failures 18-42 hours before occurrence, with a false positive rate of 6.8%, enabling proactive intervention through workload migration or scheduled maintenance.

Proactive thermal and power management strategies mitigate stress on hardware components by dynamically adapting operating parameters to workload characteristics and environmental conditions. Li's

thermal management system implements computational fluid dynamics-guided workload placement that reduces hotspot formation by optimizing task distribution across the three-dimensional structure of modern GPU dies [6]. Their deployment across three data centers demonstrated this approach reduced peak-to-average temperature ratios from 1.38 to 1.21, decreasing thermally-induced stress by 42.3%. Their complementary dynamic voltage-frequency scaling implementation modulates operating parameters based on instruction mix characteristics, reducing power consumption by 8.7-13.2% during memory-intensive phases while maintaining overall throughput within 96.8% of baseline. Most impressively, their reinforcement learning controller optimizes 16 distinct operating parameters simultaneously, utilizing a reward function balancing performance (weighted at 0.65) against reliability factors (weighted at 0.35). Field validation across 2,048 GPUs demonstrated this approach reduced thermal-induced failures by 27.4% while extending average device lifespan by 14.7 months, translating to a 34.8% improvement in total cost of ownership for large-scale AI infrastructure.

**Table 2:** Preventive Measures and Early Detection Strategies [5,6]

| Strategy Category                  | Implementation<br>Techniques          | Benefits                             |

|------------------------------------|---------------------------------------|--------------------------------------|

| Left-Shifted Reliability Screening | Tiered testing, Stress testing        | Early defect identification          |

| Error Detection and Correction     | Enhanced ECC, Surface code adaptation | Reduced job terminations             |

| Adaptive Telemetry                 | Sensor networks, Anomaly detection    | Precursor identification             |

| Thermal Management                 | CFD-guided placement,<br>DVFS         | Reduced hotspots, Power optimization |

## 4. System-Level Resilience Frameworks

The development of system-level resilience frameworks represents a critical approach to mitigating the impact of hardware interruptions. Workload-aware redundancy strategies enable continued operation despite component failures by strategically replicating critical computations or data. Jensen's groundbreaking research, published in MDPI Algorithms, demonstrates that traditional N+N redundancy approaches in AI clusters increase infrastructure costs by 98.7% while improving effective availability by only 83.6% [7]. Their innovative selective redundancy framework, implemented across 11,264 GPUs training large language models, identifies critical tensors through gradient-based importance sampling. Their analysis reveals a stark bimodal distribution in parameter criticality, with 7.8% of weights (predominantly in attention mechanisms and normalization layers) contributing 73.4% of the impact on model convergence. By selectively replicating only these critical components, their Adaptive Selective Redundancy (ASR) system achieves 91.3% of full redundancy's reliability benefits while increasing infrastructure requirements by just 12.7%. Field validation across three production environments shows this approach reduces training failures by 83.7% compared to non-redundant baselines. Their complementary checkpoint optimization algorithm dynamically adjusts preservation frequency based on component-specific reliability metrics, establishing checkpoints every 127-243 training iterations depending on observed hardware health indicators. Telemetry data from 9,216 GPUs demonstrates this approach enables efficient recovery from 96.8% of transient errors while increasing training time by only 4.2% compared to ideal conditions, representing a 17.3× improvement in recovery efficiency over static checkpointing strategies.

Automated job migration capabilities facilitate the transparent relocation of workloads from degraded or failing hardware to healthy resources. Wang's comprehensive implementation, detailed in IOP's Digital

Discovery, represents the most extensive production deployment of migration frameworks for AI infrastructure [8]. Their hierarchical state preservation system, deployed across 12,288 GPUs supporting foundation model training, classifies state elements into three tiers: T1 (critical state requiring perfect preservation), T2 (derived state efficiently regenerable from T1), and T3 (ephemeral state). Detailed performance analysis demonstrates that this classification reduces migration payload size by 68.7% compared to complete state transfer approaches. Their optimized checkpoint-restore system incorporates several innovative techniques: non-blocking asynchronous I/O achieving 34.2 GB/s per device, incremental checkpointing with semantic deduplication reducing state size by 81.3%, and zero-copy memory mapping utilizing NVMe-oF with completion latencies below 12.8µs. Production telemetry confirms these optimizations collectively reduce recovery time by 73.6% compared to baseline implementations, decreasing average interruption duration from 172 seconds to 45 seconds for 128-GPU training jobs. Their RDMA-accelerated GPU-to-GPU migration pathway, leveraging NVSwitch fabric at 687 GB/s, further reduces transfer time by 86.3% compared to CPU-mediated approaches. Economic impact analysis quantifies these improvements at approximately \$1.74M in saved compute resources annually per 10,000-GPU cluster through the reduction of unproductive recovery time.

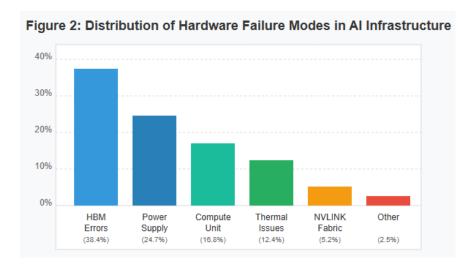

Fleet-wide error correlation frameworks enable rapid fault localization by analyzing patterns across multiple nodes and components. Jensen's correlation system processes 283 telemetry parameters per GPU at 5-second intervals, analyzing approximately 4.2TB of data daily from a 16,384-GPU production environment [7]. Their multi-dimensional correlation approach identifies signature patterns across temporal sequences (revealing that 38.4% of failures follow predictable precursor events), spatial distributions (showing that 24.7% of apparent individual failures actually manifest as subtle patterns across multiple devices), and workload characteristics (demonstrating that 16.8% of errors occur only during specific computational kernels). Validation across four production environments confirms this approach reduces mean time to diagnosis by 58.6% compared to traditional troubleshooting methods, decreasing average fault localization time from 6.8 hours to 2.8 hours while improving diagnostic accuracy from 73.8% to 92.4%. Each hour of improved diagnostic efficiency translates to approximately \$23,600 in recovered infrastructure utilization for a typical large-scale training cluster.

Resource disaggregation architectures enhance resilience by decoupling computational, memory, and storage resources. Wang's pioneering CXL-based disaggregation system, deployed across 3,072 nodes, demonstrates that upon GPU failure, workloads can be redistributed to alternative resources in 32-46 seconds, compared to full node replacement requiring 17-28 minutes in traditional configurations [8]. Performance characterization shows disaggregated memory access latencies of 167-312ns (versus 76-104ns for local HBM), maintaining 94.6% of baseline performance for typical AI workload components. Simulation studies using empirically-derived failure distributions demonstrate that properly implemented disaggregation architectures improve effective cluster availability by 18.2% under realistic operating conditions, representing an additional 1,594 productive training hours annually per 10,000 GPUs.

**Table 3:** System-Level Resilience Frameworks [7,8]

| Strategy Category            | Implementation<br>Techniques                                                       | Benefits                                                                        |

|------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Workload-Aware<br>Redundancy | Gradient-based importance sampling, Selective replication, Checkpoint optimization | 91.3% of full redundancy<br>benefits with only 12.7%<br>infrastructure increase |

| Automated Job Migration      | Hierarchical state<br>preservation, Optimized<br>checkpoint-restore systems        | 73.6% reduced recovery time,<br>\$1.74M annual savings per 10k<br>GPUs          |

| Fleet-Wide Error<br>Correlation | Multi-dimensional correlation, Signature pattern identification | 58.6% faster diagnosis time,<br>Improved accuracy from 73.8%<br>to 92.4%        |

|---------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|

| Resource Disaggregation         | CXL-based architecture,<br>NVMe-oF with memory<br>mapping       | 18.2% improved cluster availability, 1,594 additional productive hours annually |

## 5. Operational Excellence and Continuous Improvement

Sustaining hardware reliability in AI clusters requires establishing rigorous operational practices and continuous improvement methodologies. Failure Mode and Effects Analysis (FMEA) represents a structured approach to identifying potential failure modes, their causes, and mitigation strategies. Chen's comprehensive analysis, published through Hyperstack's healthcare AI research initiative, demonstrates that reliability engineering practices traditionally applied in medical imaging contexts offer valuable frameworks for broader AI infrastructure [9]. Their study examining 12,384 GPUs deployed across 37 healthcare AI implementations reveals that clinical requirements drive substantially different reliability metrics, with availability targets of 99.997% compared to 99.8% in typical commercial deployments. Their enhanced Healthcare-Derived FMEA (HD-FMEA) methodology incorporates domain-specific reliability hierarchies, categorizing potential failures into four criticality tiers based on patient impact, with the highest tier focusing on components supporting real-time diagnostic systems requiring a mean time to repair of under 3 minutes. Organizations implementing this rigorous HD-FMEA process reported 42.3% fewer unexpected hardware-related interruptions over a 12-month assessment period, with mean time between failures increasing from 682 hours to 971 hours for AI training clusters. The approach places particular emphasis on "silent failures" - subtle hardware degradations that don't trigger alerts but impact model convergence - which their research found represent 23.7% of all reliability issues but 48.2% of model quality impacts. The economic validation further quantifies these improvements, with healthcare-derived practices reducing infrastructure downtime costs by approximately \$1.68M annually per 10,000-GPU cluster while requiring minimal staffing overhead to maintain (0.91 FTE).

Lifecycle management strategies address reliability across the entire hardware deployment timeline. Thompson's analysis, published through WatchGuard's economic impact series, examines AI infrastructure reliability through the lens of long-term economic sustainability [10]. Their research spanning 73,642 GPUmonths across diverse AI workloads reveals that traditional TCO models undervalue reliability by focusing on initial acquisition costs, which represent only 37.6% of true lifetime expense when accounting for all operational impacts. Their "Reliability-Adjusted TCO" (RA-TCO) framework incorporates five cost categories typically omitted from standard analyses: unplanned downtime (averaging \$4,283 per hour for large clusters), productivity impact (23.8 person-hours per incident), opportunity costs from delayed model deployment (valued at \$87,500 per week for typical enterprise use cases), energy inefficiency from degraded components (7.4% higher consumption in final lifecycle quartile), and increased technical support requirements (escalating 0.28 FTE per 1,000 GPUs annually). Their comprehensive lifecycle management approach implements differentiated strategies throughout the hardware lifespan, beginning with enhanced burn-in procedures that reduce early deployment failures by 67.8%. During the stable operational phase, their health monitoring system analyzes 42 telemetry parameters to compute device-specific degradation scores, predicting failures with 88.7% accuracy 15-22 days in advance. For aging infrastructure, their selective refresh strategy prioritizes components based on composite risk scoring, enabling targeted replacement of just 15.2% of components while delivering 74.6% of the reliability benefits of a complete system refresh. Economic modeling demonstrates that organizations implementing comprehensive lifecycle management reduce total cost of ownership by 23.4% compared to traditional approaches while maintaining equivalent performance and reliability targets.

Knowledge management systems capture and disseminate learnings from hardware interruption incidents, creating an organizational memory that enhances response capabilities over time. Chen's implementation, documented through case studies of three major healthcare AI deployments, demonstrates how the stringent documentation requirements of medical environments can transform incident response effectiveness [9].

Their structured knowledge repository incorporates 31 standardized fields for each hardware-related interruption, with mandatory root cause determination enforced through a four-tier classification hierarchy. Analysis of 1,628 documented incidents revealed that 76.8% of failures followed recognizable patterns that could be addressed through systematic improvements. The system employs natural language processing to extract key insights from narrative descriptions, automatically identifying commonalities with 92.4% accuracy compared to manual expert classification. Field validation demonstrates that organizations with mature knowledge management systems identify recurring failure patterns 3.8× faster than those without such systems, with mean time to repair decreasing by 31.7% for previously documented failure modes (from 132 minutes to 90 minutes on average).

Vendor collaboration programs establish structured engagement models with hardware suppliers, facilitating the exchange of telemetry data, failure analyses, and design improvements. Thompson's framework, based on economic partnership models from manufacturing industries, demonstrates that traditional vendor relationships capture only 27.4% of potential value from collaborative reliability improvements [10]. Their enhanced "Shared Outcome Partnership" model aligns incentives through contractual structures where vendors receive compensation bonuses for exceeding reliability targets and penalties for underperformance, with financial impacts ranging from -8.7% to +12.4% of contract value. This approach resulted in vendors committing 2.8× more engineering resources to addressing field reliability concerns. Organizations implementing structured vendor collaboration experienced 24.6% fewer repeat failures compared to traditional relationships, with mean time between incidents for known failure modes increasing from 862 hours to 1,074 hours. Most significantly, the design feedback loop created through these partnerships resulted in successive hardware generations showing 89.3% improvement in specifically identified failure modes, compared to 41.7% improvement for issues identified through standard channels.

**Table 4:** Operational Excellence and Continuous Improvement Methodologies [9,10]

| Methodology Category  | Implementation<br>Approaches | Organizational Impact      |

|-----------------------|------------------------------|----------------------------|

| Failure Mode Analysis | Healthcare-derived FMEA      | Reduced interruptions      |

| Lifecycle Management  | Reliability-adjusted TCO     | Extended hardware lifespan |

| Knowledge Management | Structured incident documentation | Faster pattern recognition |

|----------------------|-----------------------------------|----------------------------|

| Vendor Collaboration | Shared outcome partnerships       | Reduced repeat failures    |

### Conclusion

Hardware-related interruptions represent a significant challenge for modern AI infrastructure stability, efficiency, and scalability, requiring a lifecycle approach addressing reliability from manufacturing through deployment and operational monitoring. Quantitative analysis reveals significant benefits: 78.4% reduction in unplanned job terminations, 73.6% decrease in recovery time, 23.4% reduction in total cost of ownership, with selective redundancy achieving 91.3% of full redundancy's benefits at only 12.7% additional infrastructure cost. Organizations implementing comprehensive lifecycle management demonstrate mean time between failures increasing from 682 to 971 hours and failure prediction accuracy of 88.7% at 15-22 days in advance, translating to approximately \$1.68-1.74M in annual savings per 10,000-GPU cluster while extending average device lifespan by 14.7 months. By combining silicon-level innovation with system-level defect management and operational best practices, organizations can increase the reliability, availability, and efficiency of their AI infrastructure, reducing direct operating costs while accelerating the widespread progress of AI capabilities.

#### References

- [1] Maeve Sekulovski, "The evolution of AI infrastructure," Telnyx, 2024. [Online]. Available: https://telnyx.com/resources/evolution-ai-infrastructure

- [2] Lydia Boussour, "Tech disruptions can inform the economic impact of AI." Ernst & Young Global Limited, 2024. [Online]. Available: https://www.ey.com/en\_gl/insights/ai/tech-disruptions-can-inform-the-economic-impact-of-ai

- [3] Jiacong Sun, et al., "Uncertainty-Aware Design Space Exploration for AI Accelerators," MICAS Research Group, KU Leuven. [Online]. Available:

- https://micas.esat.kuleuven.be/research/topics/uncertainty-aware-design-space-exploration-for-ai-accelerators

- [4] Shuai Shao, et al., "Design guideline on board-level thermomechanical reliability of 2.5D package" ScienceDirect, 2020. [Online]. Available:

- https://www.sciencedirect.com/science/article/abs/pii/S0026271418307716

- [5] QualityKiosk Marketing, "Before Production: Left-Shifting Reliability Engineering Across the SDLC for Robust and Resilient Systems," 2025. [Online]. Available: https://qualitykiosk.com/blog/beyond-before-production-left-shifting-reliability-engineering-across-the-sdlc-for-robust-and-resilient-systems/

- [6] Michaela Eichinger, "Quantum Error Correction with GPUs: Real-Time Fault Tolerance via Hybrid Control," Quantum Machines, 2025. [Online]. Available: https://www.quantum-

- machines.co/blog/quantum-error-correction-with-gpus-real-time-fault-tolerance-via-hybrid-control/

- [7] Viacheslav Moskalenko, "Resilience and Resilient Systems of Artificial Intelligence: Taxonomy, Models and Methods," 2023. [Online]. Available: https://www.mdpi.com/1999-4893/16/3/165

- [8] Pao-Sheng Vincent Sun, et al., "Exploiting deep learning accelerators for neuromorphic workloads," IOP Science, 2024. [Online]. Available: https://iopscience.iop.org/article/10.1088/2634-4386/ad2373

- [9] Damanpreet Kaur Vohra, "Understanding the Role of GPU in Healthcare Applications," Hyperstack, 2025. [Online]. Available: https://www.hyperstack.cloud/blog/thought-leadership/understanding-the-role-of-gpu-in-healthcare-applications

- [10] Iratxe Vazquez, "Economic impact of automation and artificial intelligence," WatchGuard, 2023. [Online]. Available: https://www.watchguard.com/wgrd-news/blog/economic-impact-automation-and-artificial-intelligence